DMA (Direct Memory Access)

AXI DMA

Stream 형식으로 데이터를 보냄

→ Streaming

- 응용 프로그램과 드라이버 간에 버퍼에 대한 포인터만 교환되고 데이터 자체는 복사되지 않는 방식

- 데이터가 연속적인 흐름으로 처리되며, 주로 Audio, Video Streaming과 같이 지속적으로 데이터가 전송되어야 하는 상황에서 사용된다.

• 주요 AXI4 데이터 폭 지원: 32, 64, 128, 256, 512, 1,024 비트

• 주요 AXI4-Stream 데이터 폭 지원: 8, 16, 32, 64, 128, 256, 512, 1,024 비트

• 선택적인 스트림 데이터 폭 최대 512비트에 대한 데이터 재정렬 엔진

기본 메모리 맵 및 스트림 데이터 경로에서 바이트(8비트) 단위로 데이터 재정렬 가능

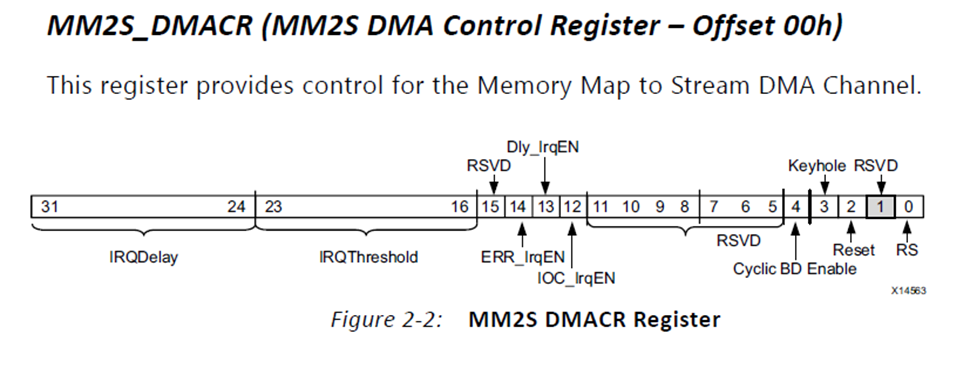

각각의 Control Regitster별 offset은 상단의 표와 같이 설정되어 있음.

주의해야 할 점이 앞서 이야기 했던 Scatter gather mode의 경우와 simple mode의 경우 offset별 담당하는 역할이 다르니 이 점 유의해서 사용해야 함.

사실 control regitster가 이렇게 표로 나타나 있지만, 사실상 api를 사용하는 입장에서는 registe별 역할을 깊게 살펴 볼 필요는 없음.

이미 api를 통해 각 registe별로 다 구현을 해 놓았기에 상황에 맞게 함수만 잘 이용해 주면 동작을 수행함.

그냥 이런 flow로 동작을 하는거구나~ 정도만 이해를 하고 넘어간다면 이후 함수를 이용하여 코드 작성함에 있어서 도움이 많이 될 것임

MM2S = Memory map to Stream

S2MM = Stream to Memory map

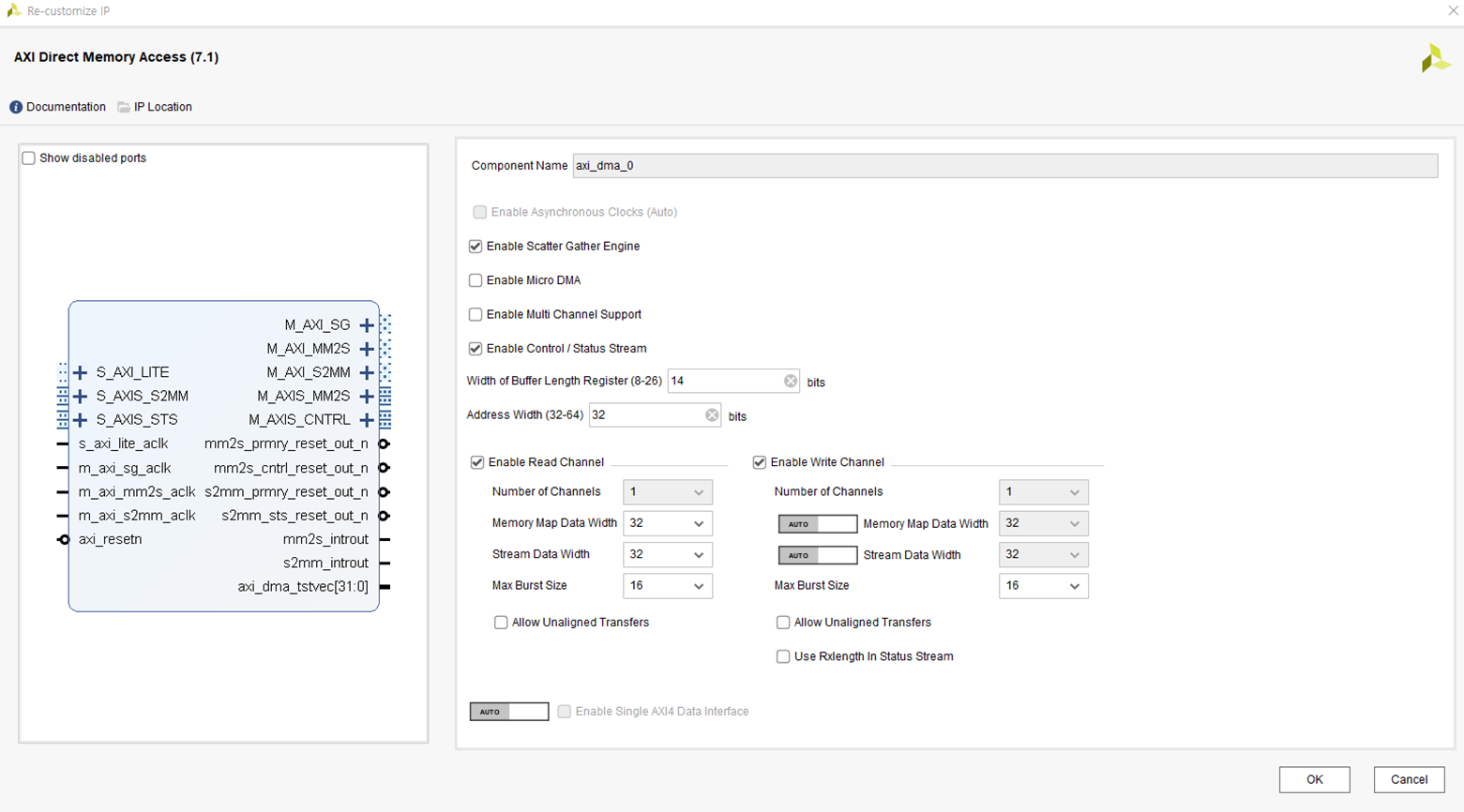

다음은 Block 내부 설정인데,

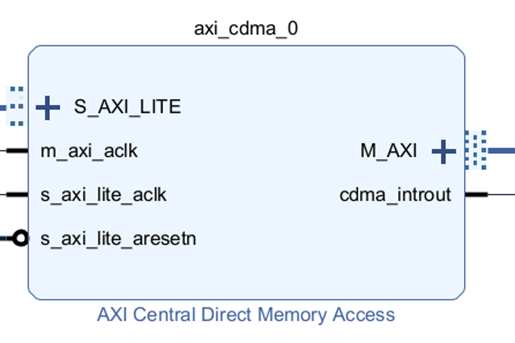

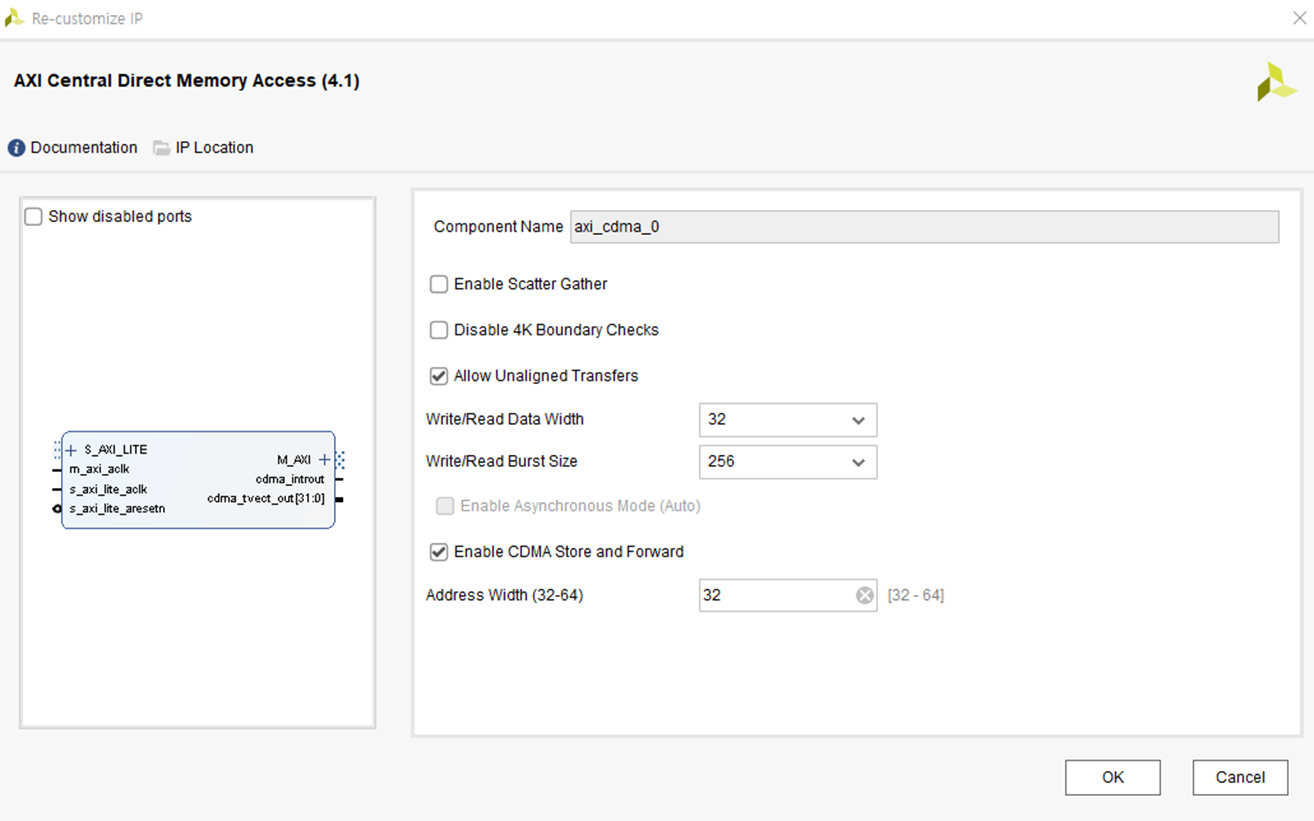

AXI CDMA

Memory map 형식으로 데이터를 보냄

→ memory mapping

- Disk에 있는 파일 일부분 또는 전체 파일을 주소 공간 내 특정 범위의 주소로 매핑하는 매커니즘

- 데이터가 메모리의 특정 주소 공간에 mapping되어 접근됨

- Hw & Sw가 서로 같은 주소 공간을 사용하여 데이터를 주고받기에 효율적임

- 이는 주로 memory & device 간의 데이터 전송에 사용됨

• 레지스터 접근을 위한 독립적인 AXI4-Lite 슬레이브 인터페이스.

° 고정된 32비트 데이터 폭

° 선택적인 비동기 작동 모드

• 주요 CDMA 데이터 경로를 위한 독립적인 AXI4 마스터 인터페이스. 32, 64, 128, 256, 512, 1,024 비트의 매개변수화 가능한 폭과 고정 주소 Burst 지원.

• 선택적인 Scatter/Gather 기능을 위한 독립적인 AXI4 마스터 인터페이스. 고정된 32비트 데이터 폭.

• 주요 CDMA 데이터 경로를 위한 선택적인 데이터 재정렬 엔진. 최대 512비트 데이터 경로 폭까지 이용 가능.

• Simple DMA 모드와 Simple DMA 및 Scatter Gather 자동화를 모두 지원하는 선택적 하이브리드 모드를 제공.

• 최대 64비트 주소 공간 지원.

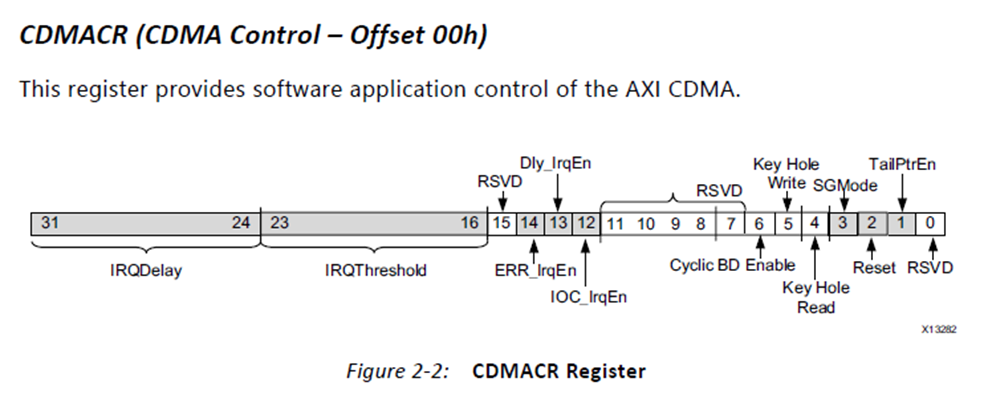

CDMA의 경우 DMA보다 offset이 확연하게 적게 형성되어 있는 것을 볼 수 있는데, 이건 Stream 형식으로 데이터를 또 보낼 필요 없기 때문임.

우측 offset을 보면 source address & destination address가 있는 걸 볼 수 있음.

앞서 말했던 source & destination 주소 값을 함수에서 설정해준다면, 해당 offset 위치에 맞게 값이 설정되는 것임.

32bit를 초과하면 다음 offset으로 넘어간 다는 것을 보여주는 것.

DMA와 마찬가지로 Scatter Gather mode가 최 상단에 위치함

사용자 기호에 맞게 체크표시 하지 않아도 된다.

Allow Unaligned Transfers

Enable CDMA Store and Forward

+) Burst를 꼭 해줘야 속도 향상이 높아짐.

[原创]Zynq AXI-CDMA的使用 - FPGATopic - 博客园

[原创]Zynq AXI-CDMA的使用 - FPGATopic - 博客园

Xilinx 提供了3种DMA AXI-DMA AXI-CDMA AXI-VDMA 使用CDMA能够满足项目需求(MM-MM),DS文档介绍如下: The Xilinx LogiCORE™ IP AXI Central Direct Memory Access (CDMA) core is

www.cnblogs.com

OS기반을 사용하는 경우에는 mmap() 함수를 이용하고,

Standalone을 사용하는 경우에는 AxiCdma를 이용함

AXI CDMA Linux user space example on Zynq UltraScale+ RFSoC

This blog entry will show you how to create an AXI CDMA Linux userspace example application. The example design will transfer data from the PS DDR to the AXI BRAM through the AXI CDMA on a Zynq UltraScale+ RFSoC ZCU111 Evaluation Kit. Applicable Platfor

support.xilinx.com

현재 전체적인 Block diagram

전체적인 Block Diagram은 다음과 같음.

이전에 Ethernet을 하면서 사용된 Diagram과 차이가 보이는 것은 CDMA가 추가됐다는 점 정도?

이때 눈여겨 봐야할 것은 CDMA의 출력 Master_AXI 단자와 연결된 Interconnect를 보면, Master 단자가 두 개로 나타난 것을 볼 수 있음.

이게 바로 CDMA를 통해서 데이터를 전달할 Block들을 연결하기 위한 통로 라고 생각해주면 됨.

연결하고 싶은 수 만큼 연결 가능하며, 위의 예제에서 보았듯 여러 개의 BRAM과 연결할 수 있음.

나는 DDR과 BRAM에 연결해주었음.

여기서 DDR = Zynq의 HP port와 연결되는 것을 의미하고, BRAM은 BRAM controlle를 통해 연결시켜 주었음.

또한, 이렇게 설정된 경우, BRAM 주소값의 경우 ps와 직접적인 연결성이 없기 때문에 추후 vitis 내에서 debugging을 진행할 때 tool을 이용해서 디버깅을 하기 어려움.

따라서 ILA를 통해 BRAM에도 제대로 값이 들어갔는지 확인하고자 추가해주었음.

PS DDR에 잘 들어가는지 확인하기 위한 것

올바르게 들어간 것을 확인할 수 있다.

BRAM의 경우 WVALID & BVALID가 High 되는 순간으로 ILA의 Timing을 잡아줌으로써 데이터 전송을 확인했다.

[일단 도움이 돼 보이는 자료 모두 넣어보기]

- [인공지능 가속기 설계] Artificial Intelligence Accelerator Design (Using Zynq-7000 FPGA, CDMA, AXI)AMD Customer CommunityDLIC 2020 HW - HackMD.

- AMD Customer Community

- Working with DMA through AXI between DDR and PL BlockRAM

- [原创]Zynq AXI-CDMA的使用 - FPGATopic - 博客园

- AMD Customer Community

CDMA is not transfering data from BRAM to DDR

support.xilinx.com

[原创]Zynq AXI-CDMA的使用 - FPGATopic - 博客园

Xilinx 提供了3种DMA AXI-DMA AXI-CDMA AXI-VDMA 使用CDMA能够满足项目需求(MM-MM),DS文档介绍如下: The Xilinx LogiCORE™ IP AXI Central Direct Memory Access (CDMA) core is

www.cnblogs.com

Working with DMA through AXI between DDR and PL BlockRAM

Hello Everyone, My peers in Path to Programable have Done Great work in giving step by step procedure to implement DMA transfer so Why Reinvent the Wheel , I take a different approach.I will try to present a vivid picture regarding Why we need to implement

community.element14.com

Using AXI CDMA to write from OCM/DDR to BRAM

support.xilinx.com

AXI CDMA Linux user space example on Zynq UltraScale+ RFSoC

This blog entry will show you how to create an AXI CDMA Linux userspace example application. The example design will transfer data from the PS DDR to the AXI BRAM through the AXI CDMA on a Zynq UltraScale+ RFSoC ZCU111 Evaluation Kit. Applicable Platfor

support.xilinx.com

ps) Notion에 정리하며 적은 글이라 완성도가 높지 않음을 양해 바랍니다.. :( ㅠㅠ

'대학원 > 대회 준비 관련' 카테고리의 다른 글

| [Vitis] Build 오류, Xilinx Vitis arm-xilinx-eabi-cc.exe: error: *.c: Invalid argument (2) | 2024.07.03 |

|---|---|

| plt.pcolormesh 함수 확인하기 (0) | 2024.06.18 |

| [ZCU-104]DMA + echo (0) | 2024.06.11 |

| [ZCU-104]AXI DMA Scatter Gather (1) | 2024.05.28 |

| [ZCU-104]DMA + DDR 공부 내용 (0) | 2024.05.28 |