대회준비 나름 한다고 열심히는 했는데, 예선에서 광탈해버렸다.

우리보다 실력이 뛰어난 사람이 이렇게 많구나를 다시금 느낄 수 있었다.

그래도 대회 준비를 하면서 반년 전에 비해 실력이 꽤 올랐다는 것은 체감하고 있으니.. 우선은 이걸로 만족하고 남은 취준과 석사 학기를 잘 마무리 해 볼 계획이다

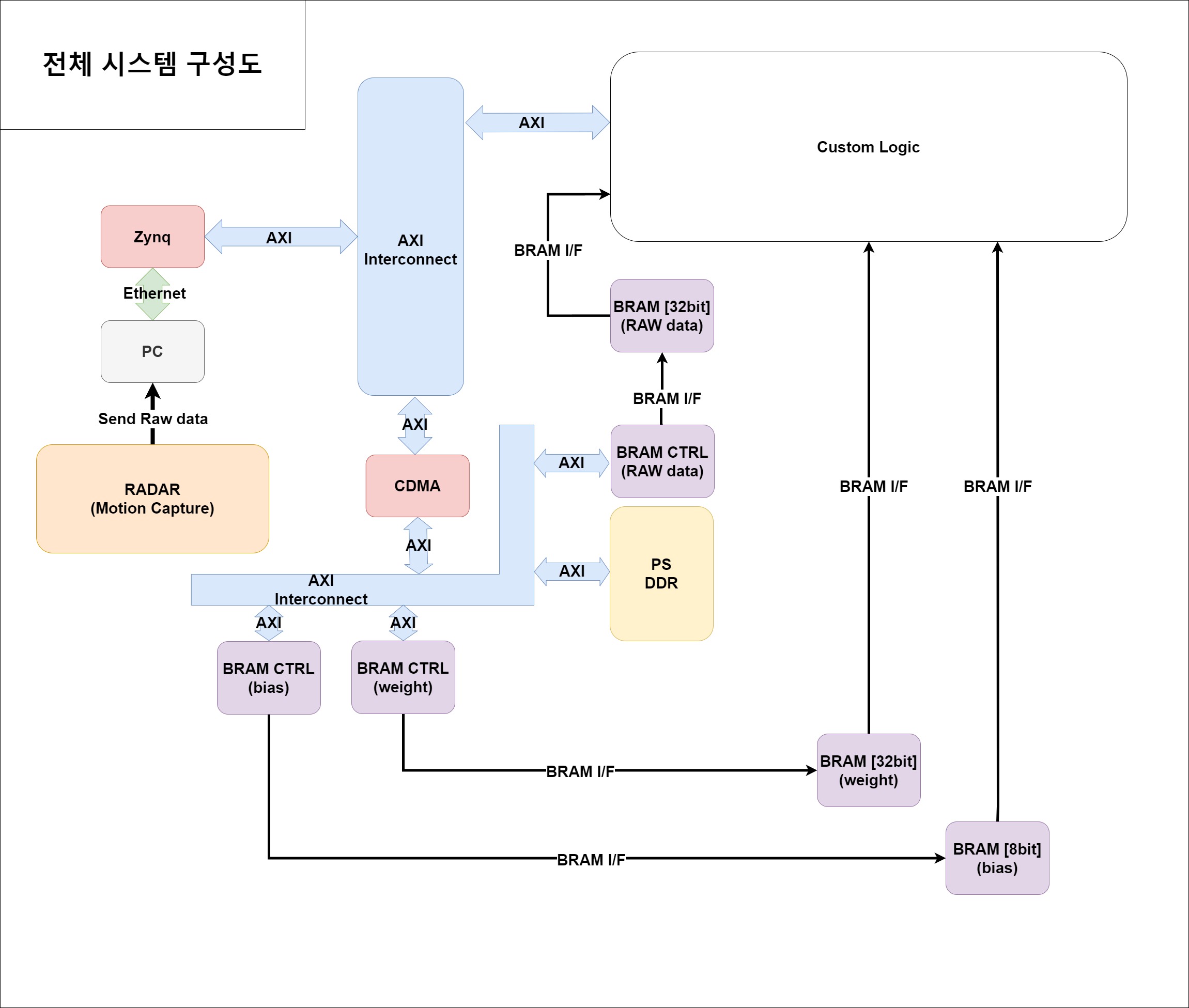

우선 전체적으로 구성했던 프로그램부터 설명하자면,

다음 그림과 같이 구성을 했다.

PS, 즉 ARM-Core 영역에서 건들일 부분은 CDMA와 Ethernet을 이용해 데이터를 넘겨주는 부분이었다.

이 두 과정은 앞선 포스팅들에 어느정도 정리를 해둔 방식을 토대로 진행했고, 최종적으로 Custom ip를 연결할 때 약간씩 수정을 하여 VITIS 코드를 완성했다.

아래부터 적을 내용은 Custom ip에서 사용될 RAW & WEIGHT & BIAS 를 BRAM 혹은 URAM에 어떻게 할당할 지 적은 내용과 이를 검증한 방식에 대한 내용이다.

추가로, 본 custom ip의 register map은 다음과 같다.

* 먼저 우리는 URAM을 사용했는데, 이를 사용한 이유는 weight를 담는데 있어서 bram보다 크기가 큰 memory i/f를 사용하기 위해서였다.

처음에는 ROM 형식으로 사용하고자 했으나, URAM은 ROM으로서 사용이 불가하여 처음에 제안했던 bram 형식으로 돌아와 다시 프로젝트를 구현했다.

그러기위해 각각의 필요한 메모리 크기를 정해줬어야 했는데,

weight의 txt파일 크기 (distance 1개당 163,792 x 32bit)

→ 640번 반복

bias의 txt파일 크기 (distance 1개당 633 x 32bit)

→ 3번 반복

Raw 데이터의 txt파일 크기 (256 x 256 x 8bit), (65,636 x 8bit)

→ 64번 반복

이와같은 "반복" 이라는 단어는 Ethernet 데이터를 송수신 함에 있어서 최대 전송 가능 byte 수가 1500 수준이기에, 그냥 보기 쉽게 1024 byte씩 나눠서 보내주었다.

따라서 이로인해 발생하는 총 데이터 전송을 위해 반복해야 하는 전송 횟수를 의미한다.

1024byte(8bit) = 1024/4 = 256

모든 memory data는 각각의 bram에 모두 잘 옮겨진 것 같았으나, vitis 동작에 있어서 오류가 발생했었다.

아래는 이를 해결하는 과정을 적은 내용이다.

오류

다음 segment로 넘어가지 않음.

이는 단순하게 말하면 FSM에서 다음 상태로 넘어가지 않는 문제였고, 해결하기 위해 ILA를 적극 활용해보았다.

[RAW file]

checking_file_header = 254, now_buf = 16055560

8128/

[WEIGHT file]

checking_file_header = 75, now_buf = 2409241

내꺼 마지막 = 1011f

+97968

1ff3c

내가 보고싶은 것 = dense layer 0 의 1/4 지점 weight 마지막 값이 잘 들어갔는지.

dense layer 0 → 1/4 지점 주소값 = 1BEAF

내 쪽도 잘 읽히고 있음.

근데 이쪽에서 값이 왜 이러지? 얘가 이렇게 튀면 안 되지 않나? Modelsim하고 값 비교를 해봐야 할 듯.

(동일하게 나오는 것이라 문제 없던 부분임)

[RAW file]

동일하게 읽히는 중

64면 64 * 4 = 256이니깐, 아마 요구한 수준으로 읽고 있는 것이 맞을 것임.

클럭 속도 차이인가?

-> 근데 또, PS & PL 간의 속도 차이가 있어도 문제가 되는 것 같지는 않음..

enable_out을 6clk 늘리니 되긴 함.

그럼 2번째 seg_enable도 제대로 되고 있는건지 확인해봐야 할듯?

마지막 enable이 나오지 않음.

일단 10clk enable로 변경해서 다시 동작해볼 예정.

SEG_Enable이 나오긴 함.

특별히 바꾼건 없는데 왜 나오는건지는 아직 이해가 안가네..

다시 또 안됨.

결국 안됐던 이유는 AXI_LITE RDATA를 확인하기 위해서는 RVALID & RREADY 신호가 들어가는 그 순간에만 데이터를 챌 수 있음.

그런데 지금까지는 그 전에 채가지고 문제가 발생한거같음.

그래서 keep delay를 25 정도로 줬더니 원활하게 동작함.

최종적으로 요구한 동작에 맞는 결과물을 pc에서 수신 가능했음.

이로서 최종 프로젝트..

석사 기간동안 해볼 수 있는 가장 볼륨이 큰 팀 프로젝트를 처음이자 마지막으로 마무리했다.

최종적으로 성과라는 결과물이 나왔더라면 더 좋았겠지만... 아쉬움이 남긴하네

그래도 덕분에 취준에 쓰일 자소서 거리는 꽤 만든 것 같아서 약간은 뿌듯하다.

아마 당분간은 특별한 포스팅은 없지 않을까 싶다.

GSAT & 자소서 준비 등만 하다보니 글을 적을 내용이 없다보니.. 일단은 저 부분에 다시 또 집중이나 하자.

아, 어쩌면 요즘 읽고 있는 책의 후기를 적을수도..?

'대학원 > 대회 준비 관련' 카테고리의 다른 글

| [Vitis] Build 오류, Xilinx Vitis arm-xilinx-eabi-cc.exe: error: *.c: Invalid argument (3) | 2024.07.03 |

|---|---|

| plt.pcolormesh 함수 확인하기 (0) | 2024.06.18 |

| DMA vs CDMA (1) | 2024.06.14 |

| [ZCU-104]DMA + echo (0) | 2024.06.11 |

| [ZCU-104]AXI DMA Scatter Gather (2) | 2024.05.28 |